香港中文大學

The Chinese University of Hong Kong

## CENG3430 Rapid Prototyping of Digital Systems Lecture 01: Introduction to VHDL

#### Ming-Chang YANG mcyang@cse.cuhk.edu.hk

## Outline

- Basic Structure of a VHDL Module

- 1) Library Declaration

- 2) Entity Declaration

- External Signal (I/O Pins)

- 3) Architecture Body

- Internal Signal

- Architectural Design Methods

- ① Data Flow Design (concurrent statements)

- ② Structural Design ("port map")

- ③ Behavioral Design (sequential statements)

- Concurrent vs. Sequential Statements

- Design Constructions

## **Basic Structure of a VHDL Module**

#### A VHDL file

#### 1) Library Declaration

library IEEE; use IEEE.std\_logic\_1164.all; use IEEE.std\_logic\_arith.all; use IEEE.std\_logic\_unsigned.all;

#### 2) Entity Declaration

Define the <u>signals</u> that can be seen outside <u>externally</u> (I/O pins)

#### 3) Architecture Body

Define the <u>internal signals and</u> <u>operations</u> of the desired function

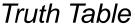

# Example: 4-bit Comparator in VHDL (1/2)

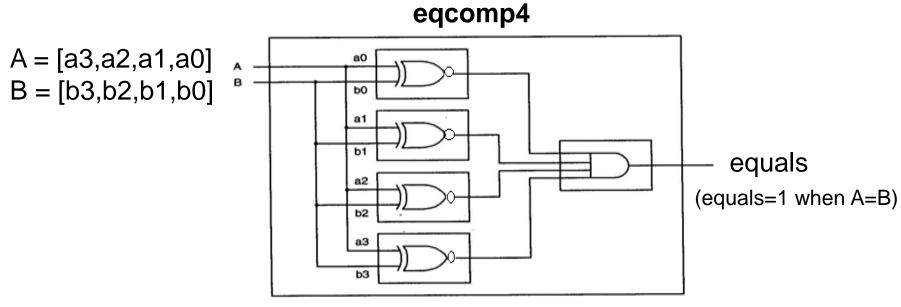

Schematic Circuit of a 4-bit Comparator

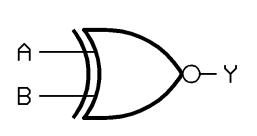

- \*Recall: Exclusive NOR (XNOR)

- When A=B, Output Y = 0

- Otherwise, Output Y = 1

| Α | В | Y |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

VHDL for programmable logic, Skahill, Addison Wesley

# Example: 4-bit Comparator in VHDL (2/2)

Code of 4-bit Comparator in VHDL:

| eqcomp4.vh           | d  |                                                         |

|----------------------|----|---------------------------------------------------------|

|                      | 1  | the code starts here , "a comment"                      |

| Library              | 2  | library IEEE;                                           |

| Declaration          | 3  | use IEEE.std_logic_1164.all;                            |

|                      | 4  | entity eqcomp4 is                                       |

| Entity               | 5  | <pre>port (a, b: in std_logic_vector(3 downto 0);</pre> |

| Declaration          | 6  | equals: out std_logic);                                 |

|                      | 7  | end eqcomp4;                                            |

|                      | 8  | architecture arch_eqcomp4 of eqcomp4 is                 |

| Angleite stung       | 9  | begin                                                   |

| Architecture<br>Body | 10 | equals <= '1' when $(a = b)$ else '0';                  |

| Dody                 | 11 | "comment line"                                          |

|                      | 12 | end arch_eqcomp4;                                       |

|                      |    |                                                         |

## Outline

- Basic Structure of a VHDL Module

1) Library Declaration

- 2) Entity Declaration

- External Signal (I/O Pins)

- 3) Architecture Body

- Internal Signal

- Architectural Design Methods

- ① Data Flow Design (concurrent statements)

- ② Structural Design ("port map")

- ③ Behavioral Design (sequential statements)

- Concurrent vs. Sequential Statements

- Design Constructions

# **Entity Declaration**

## **Identifiers**

- Identifiers: Used to name any object in VHDL

- Naming Rules:

- 1) Made up of only <u>alphabets</u>, <u>numbers</u>, and <u>underscores</u>

- 2) First character must be a letter

- 3) Last character CANNOT be an underscore

- 4) <u>Two</u> connected <u>underscores</u> are NOT allowed

- 5) <u>VHDL-reserved words</u> are **NOT** allowed

- 6) VHDL is NOT case sensitive

- Txclk, Txclk, TXCLK, TxClk are all equivalent

## **VHDL Reserved Words**

| abs<br>access<br>after              | file<br>for<br>function        | of<br>on<br>open               | select<br>severity<br>shared |

|-------------------------------------|--------------------------------|--------------------------------|------------------------------|

| alias<br>all<br>and<br>architecture | generate<br>generic<br>guarded | or<br>others<br>out            | signal<br>sla<br>sll<br>sra  |

| array<br>assert<br>attribute        | if<br>impure                   | package<br>port<br>postponed   | srl<br>subtype               |

| begin<br>block                      | in<br>inertial<br>inout        | procedure<br>process<br>pure   | then<br>to<br>transport      |

| body<br>buffer<br>bus               | is<br>label                    | range<br>record                | type<br>unaffected           |

| case<br>component<br>configuration  | library<br>linkage<br>literal  | register<br>reject<br>rem      | units<br>until<br>use        |

| disconnect                          | loop<br>map<br>mod             | report<br>return<br>rol<br>ror | variable<br>wait             |

| downto                              | nand<br>new                    | 101                            | when<br>while<br>with        |

| elsif<br>end<br>entity              | next<br>nor<br>not             |                                | xnor<br>xor                  |

| exit                                | null                           |                                |                              |

# **Class Exercise 1.1**

- Determine whether the following identifiers are legal or not. If not, please give your reasons.

- tx\_clk

- \_tx\_clk

- Three\_State\_Enable

- 8B10B

- sel7D

- HIT\_1124

- large#number

- link\_\_\_bar

- select

- rx\_clk\_

# External Signals (I/O Pin)

- An external signal (or I/O pin) is a physical wire that can carry logic information.

- Many logic types are eligible for external signals, e.g.,

- bit: logic '1' or '0' only

- **std\_logic**: 9-valued standard logic (IEEE standard 1164)

| 'U' | Uninitialized                      | ""  | Don't care   |

|-----|------------------------------------|-----|--------------|

| 'X' | Forcing unknown                    | 'W' | Weak unknown |

| "0" | Forcing 0                          | "L" | Weak 0       |

| "1" | Forcing 0                          | 'H' | Weak 1       |

| 'Z' | High impedance (or floating state) |     |              |

• E.g., equals: out std\_logic;

- std\_logic\_vector: a group of wires (i.e., a signal bus)

• E.g., a, b: in std\_logic\_vector(3 downto 0);

- Each of a (3), a (2), a (1), a (0) is a std\_logic signal.

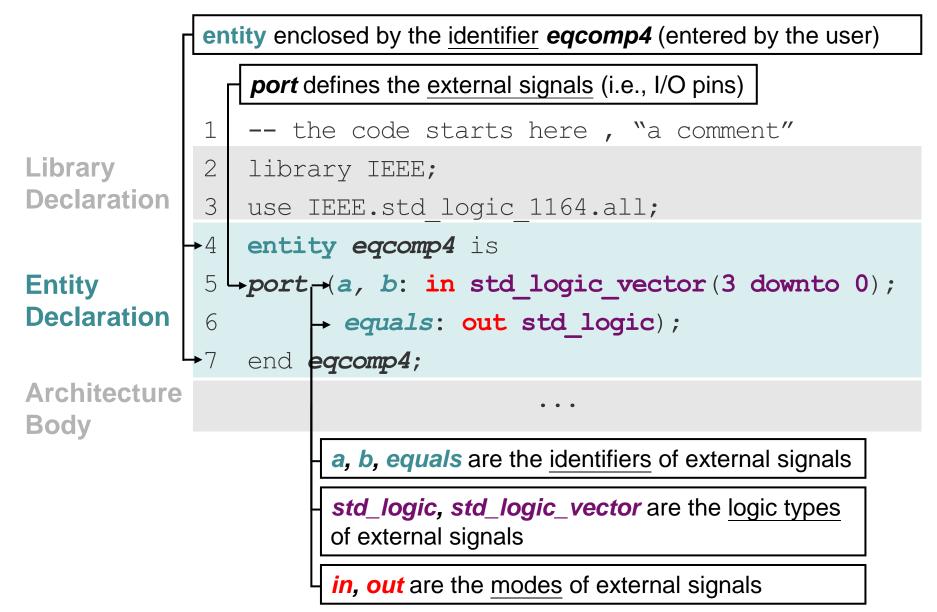

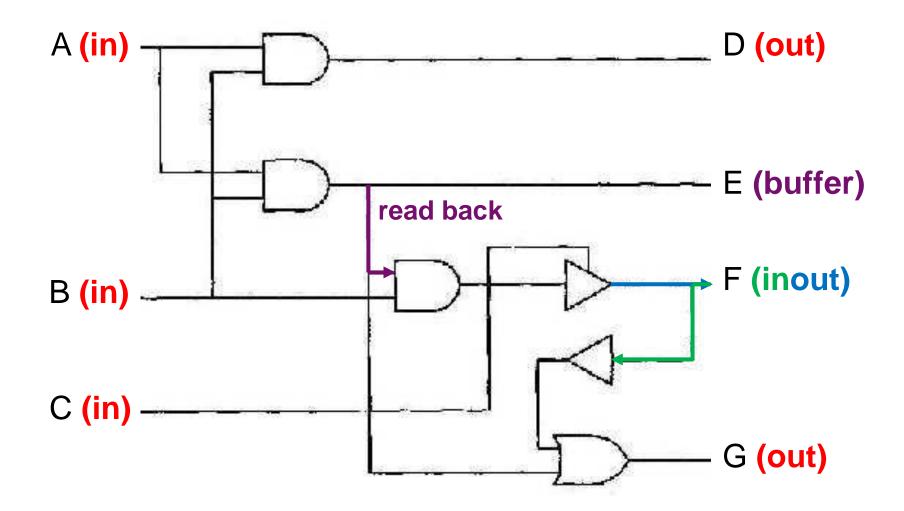

# Modes of I/O Pins (1/2)

Modes of I/O pin must be <u>explicitly specified</u> in port of entity declaration:

Example:

entity eqcomp4 is

port (a, b: in std\_logic\_vector(3 downto 0);

equals: out std\_logic);

end eqcomp4;

- There are 4 available modes of I/O pins:

- 1) in: Data flows in only

- 2) out: Data flows out only (cannot be read back by the entity)

- 3) inout: Data flows bi-directionally (i.e., in or out)

- 4) buffer: Similar to out but it can be read back by the entity

VHDL for programmable logic, Skahill, Addison Wesley

## **Class Exercise 1.2**

#### • How many input/output pins are defined in *eqcomp4*?

|                      | 1 | the code starts here , "a comment"                      |

|----------------------|---|---------------------------------------------------------|

| Library              | 2 | library IEEE;                                           |

| Declaration          | 3 | use IEEE.std_logic_1164.all;                            |

|                      | 4 | entity eqcomp4 is                                       |

| Entity               | 5 | <pre>port (a, b: in std_logic_vector(3 downto 0);</pre> |

| Declaration          | 6 | equals: out std_logic);                                 |

|                      | 7 | end <b>eqcomp4;</b>                                     |

| Architecture<br>Body |   | • • •                                                   |

## Outline

- Basic Structure of a VHDL Module

- 1) Library Declaration

- 2) Entity Declaration

- External Signal (I/O Pins)

- 3) Architecture Body

- Internal Signal

- Architectural Design Methods

- ① Data Flow Design (concurrent statements)

- ② Structural Design ("port map")

- ③ Behavioral Design (sequential statements)

- Concurrent vs. Sequential Statements

- Design Constructions

## **Architecture Body**

- Architecture Body: Defines the internal of the chip Example: the architecture body of the entity eqcomp4

architecture arch\_eqcomp4 of eqcomp4 is

begin

```

equals <= '1' when (a = b) else '0';

```

```

-- "comment line"

```

```

end arch_eqcomp4;

```

- arch\_eqcomp4: the architecture identifier (entered by the user)

- equals, a, b: I/O pins designed by the user in the entity declaration

- begin ... end: define the internal operation

- equals <= '1' when (a = b) else '0';

- <= <u>here means "signal assignment" not "less than or equal".</u>

- VHDL is strongly-typed: Signals of <u>different base types</u> CANNOT be assigned to each other without the use of type-conversion.

- <u>when-else</u> is a <u>concurrent design construction</u>.

- = is the <u>built-in operator</u> "equal".

## **Built-in Operators**

- Logical Operators: and, or, nand, nor, xor, xnor, not have their usual meanings.

- Relation Operators (result is Boolean)

- = equal

- /= not equal

- < less than

- <= less than or equal

- > greater than

- >= greater than or equal

- Logical Shift and Rotate

- sll shift left logical, fill blank with 0

- srl shift right logical, fill blank with 0

- rol rotate left logical, circular operation

- E.g., "10010101" rol 3 is "10101100"

- **ror** rotate right logical, circular operation

https://www.oreilly.com/library/view/vhdl-for-logic/9780470688472/chapter05.html

## Outline

- Basic Structure of a VHDL Module

- 1) Library Declaration

- 2) Entity Declaration

- External Signal (I/O Pins)

- 3) Architecture Body

- Internal Signal

- Architectural Design Methods

- ① Data Flow Design (concurrent statements)

- ② Structural Design ("port map")

- ③ Behavioral Design (sequential statements)

- Concurrent vs. Sequential Statements

- Design Constructions

#### Keys to design complicated architecture body!

# **Internal Signal**

- The entity declares the external signals.

- The architecture body can also declare signals that can be used internally.

architecture arch\_eqcomp4 of eqcomp4 is

-- Internal signals shall be declared here! begin

```

end arch eqcomp4;

```

- Signal: Represent physical wires

- E.g., signal s1: BIT := '1';

- Constant: Hold unchangeable values

- E.g., constant c1: BIT := '1';

#### signal SIG\_NAME: <type> [:= <value>];

Note: Signals can be declared without initialized values.

- Examples:

- signal SIG\_NAME: STD\_LOGIC;

- Declared without initialized value

- signal SIG\_NAME: STD\_LOGIC := '1';

- Signals can be declared

- In the "port" of the entity declaration (as external signals);

- Or in the architecture body (as internal signals).

constant CONST\_NAME: <type> := <value>;

Note: Constants must be declared with initialized values.

- Examples:

- constant CONST\_NAME: STD\_LOGIC := 'Z';

- constant CONST\_NAME: STD\_LOGIC\_VECTOR (3

downto 0) := "0-0-";

- '-' means "don't care"

- Constants can be declared in

- Anywhere allowed for declaration.

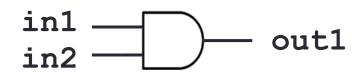

# **Class Exercise 1.3**

| 1F | S) |

|----|----|

|    |    |

```

entity nandgate is

1

2

port (in1, in2: in STD LOGIC;

3

out1: out STD LOGIC);

end nandgate;

4

5

architecture nandgate arch of nandgate is

6

7

begin

connect1 <= in1 and in2;</pre>

8

9

out1<= not connect1;</pre>

end nandgate arch;

10

```

- Declare an internal signal named "connect1" in Line 6.

- Can you assign an I/O mode to this signal? Why?

## Outline

- Basic Structure of a VHDL Module

- 1) Library Declaration

- 2) Entity Declaration

- External Signal (I/O Pins)

- 3) Architecture Body

- Internal Signal

- Architectural Design Methods

- ① Data Flow Design (concurrent statements)

- ② Structural Design ("port map")

- ③ Behavioral Design (sequential statements)

- Concurrent vs. Sequential Statements

- Design Constructions

# ① Data Flow (Concurrent Statements)

- Data flow design uses "concurrent statements" rather than "sequential statements" (see behavioral design).

- Concurrent statements can be interchanged freely.

- There's no "execution order" for concurrent statements.

```

1 library IEEE; %Vivado2014.4 tested ok

use IEEE.STD LOGIC 1164.ALL;

2

entity eqb comp4 is

3

port (a, b: in std logic vector(3 downto 0);

4

equals, bigger: out std logic);

5

end eqb comp4;

6

architecture dataflow4 of eqb comp4 is

begin

8

equals <= '1' when (a = b) else '0'; --concurrent

9

10 bigger <= '1' when (a > b) else '0'; --concurrent

11

end dataflow4;

```

CENG3430 Lec01: Introduction to VHDL 2022-23 T2

Lines 9 & 10 will be executed whenever signal a or b (or both) changes. 27

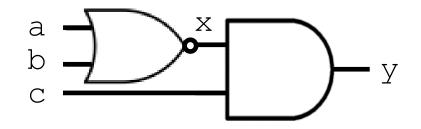

# **Class Exercise 1.4**

- Draw the schematic circuit of this code:

- 1 library IEEE; --Vivado 14.4

- 2 use IEEE.STD\_LOGIC\_1164.ALL;

- 3 entity abc is

- 4 port (a,b,c: in std\_logic;

- 5 y: out std\_logic);

- 6 end abc;

- 7 architecture abc\_arch of abc is

- 8 signal x : std\_logic;

- 9 begin

- 10 x <= a nor b;

- 11  $y \leq x$  and c;

- 12 end abc\_arch;

# Answer:

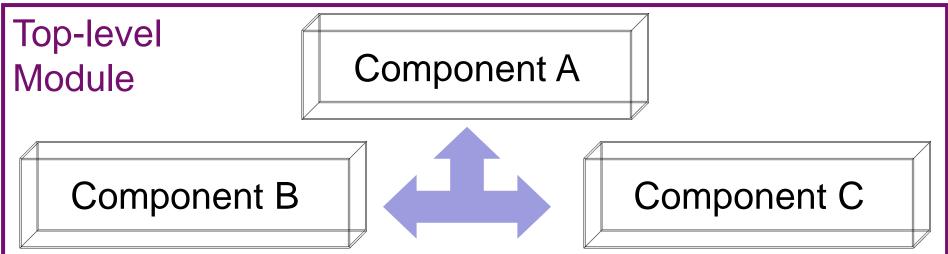

# ② Structural Design (use "port map")

• Structural Design: Like a circuit but describe it by text.

Connected by **port map** in the architecture body of the top-level design module

#### Design Steps:

Step 1: Create entities

Step 2: Create components from entities

Step 3: Use "port map" to relate the components

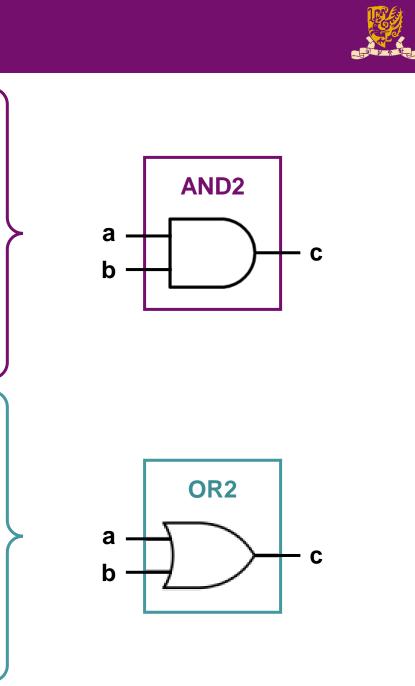

## **Step 1: Create Entities**

1 library IEEE; 2 use IEEE.STD LOGIC 1164.ALL; 3 entity and2 is 4 port (a,b: in STD LOGIC; 5 c: out STD LOGIC ); 6 end and2; 7 architecture and2 arch of and2 is 8 begin c <= a and b;9 10 end and2 arch; \_\_\_\_\_ 11 12 library IEEE; 13 use IEEE.STD LOGIC 1164.ALL; 14 entity or2 is 15 port (a,b: in STD LOGIC; c: out STD LOGIC ); 16 17 end or2; 18 architecture or2 arch of or2 is 19 begin 20 c <= a or b; 21 end or2 arch; CENG3430 Lec01: Introduction to VHDL 2022-23 T2

### **Step 2: Create Components**

component and2 --create components- port (a,b: in std\_logic; c: out std\_logic);

end component;

component or2 --create components- port (a,b: in std\_logic; c: out std\_logic);

end component;

a b b

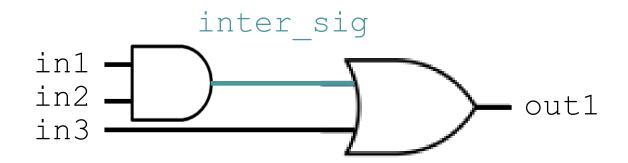

## **Step 3: Connect Components**

label1 & label 2 are line labels

begin

→ label1: and2 port map (in1, in2, inter\_sig);

→ label2: or2 port map (inter\_sig, in3, out1);

end test\_arch;

Lines can be interchanged for the same circuit design.

# Put Together: A Running Example

| 1  | library IEEE;                             | 1    | library IEEE; Top-level Module                          |

|----|-------------------------------------------|------|---------------------------------------------------------|

| 2  | use IEEE.STD_LOGIC_1164.ALL;              | 2    | use IEEE.STD_LOGIC_1164.ALL;                            |

| 3  | entity and2 is Step 1                     | 3    |                                                         |

| 4  | port (a,b: in STD_LOGIC;                  | 4    | entity test is                                          |

| 5  | c: out STD_LOGIC );                       | 5    | <pre>port ( in1: in STD_LOGIC; in2: in STD_LOGIC;</pre> |

| 6  | end and2;                                 | 6    | in3: in STD_LOGIC;                                      |

| 7  | architecture and2_arch of and2 is         | 7    | out1: out STD_LOGIC );                                  |

| 8  | begin                                     | 8    | end test;                                               |

| 9  | $c \ll a and b;$                          | 9    | architecture test_arch of test is                       |

| 10 | end and2_arch;                            | 10   | component and 2create component Step 2                  |

| 11 |                                           | 11   |                                                         |

| 12 | library IEEE;                             | 12   | end component ;                                         |

| 13 | use IEEE.STD_LOGIC_1164.ALL;              | 13   | component or2create component                           |

| 14 | entity or2 is Step 1                      | 14   | <pre>port (a,b: in std_logic; c: out std_logic);</pre>  |

| 15 | port (a,b: in STD_LOGIC;                  | 15   | end component ;                                         |

| 16 | c: out STD_LOGIC );                       | 16   | signal inter_sig: std_logic;                            |

| 17 | end or2;                                  | 17   | begin Step 3                                            |

| 18 | architecture or2_arch of or2 is           | 18   | <pre>label1: and2 port map (in1, in2, inter_sig);</pre> |

| 19 | begin                                     | 19   | <pre>label2: or2 port map (inter_sig, in3, out1);</pre> |

| 20 | $c \ll a \text{ or } b;$                  | 20   | end test_arch;inter_sig                                 |

|    | end or2_arch;                             |      | in1 out1                                                |

| CE | NG3430 Lec01: Introduction to VHDL 2022-2 | 23 T | in3 34                                                  |

## **Class Exercise 1.5**

- Draw the schematic diagram for the statements:

i label\_u0: and2 port map (a, c, x);

ii label\_u1: or2 port map (b, x, y);

- When will Lines i and ii be executed?

- Answer:

- Line i:

- Line ii:

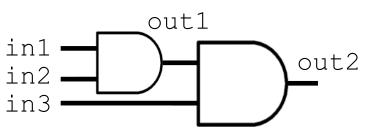

# **Another Running Example**

out1

```

entity test and and 2 is

inter sig

port ( in1: in STD LOGIC;

in1

in2

in2: in STD LOGIC;

in3

in3: in STD LOGIC;

out1: out STD LOGIC

);

end test and and 2;

architecture test and and 2 arch of test and and 2 is

component and2

No need to create the

component for the same

port (a, b: in std_logic; c: out std_logic);

entity for several times

end component ;

signal inter sig: std logic;

begin

But you can use

label1: and2 port map (in1, in2, inter sig);

the component

label2: and2 port map (inter sig, in3, out1);

multiple times

end test andand2 arch;

```

## **② Structural vs. ① Data Flow**

#### **②** Structural

("port map")

```

port (a,b: in std_logic;

```

```

c: out std_logic);

```

```

end component ;

```

```

signal x: std_logic;

```

begin

```

label1: nor2 port map (a, b, x);

label2: and2 port map (x, c, y);

```

end test\_arch;

CENG3430 Lec01: Introduction to VHDL 2022-23 T2

#### ① Data Flow

#### (concurrent statements)

```

architecture test_arch of test is

signal x : std_logic;

begin

x <= a nor b;

y <= x and c;</pre>

```

```

end test_arch;

```

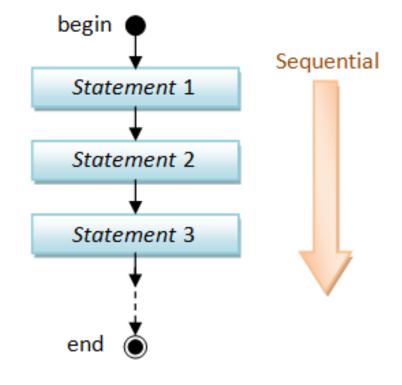

# ③ Behavioral Design (use "process")

- Behavioral design uses "sequential statements".

- Just like a sequential program

- The keyword is "process":

- The main character is "process (sensitivity list)".

- A process is executed when one (or more) of the signals in the sensitivity list changes.

- Statements inside a process are sequentially executed.

# **Behavioral Design Example**

```

library IEEE; --vivado14.4

use IEEE.STD_LOGIC_1164.ALL;

entity eqcomp4 is

port (a, b: in std_logic_vector(3 downto 0);

equals: out std_logic);

end eqcomp4;

architecture behavioral of eqcomp4 is

begin

```

```

begin

if a = b then

equals <= '1';

else

equals <= '0';

end if;

```

#### end process;

```

end behavioral;

```

#### Sequential Execution:

Statements inside a process are sequentially executed.

## Another Example? See Lab01

#### Hardware

#### Simulation

architecture Behavioral of AND TEST is

```

entity AND_Gate is

port ( A: in STD_LOGIC;

B: in STD_LOGIC;

C : out STD_LOGIC);

end AND_Gate;

architecture AND_arch of

AND_Gate is

begin

C <= A and B;

end AND_arch;</pre>

```

- 1) It is legal to have a process WITHOUT a **sensitivity list**.

- Such process MUST have some kinds of time-delay or wait (see Lec03 for more examples).

#### CENG3430 Lec01: Introduction to VHDL 2022-23 Tand Behavioral;

```

ai <= '0'; bi <= '0';

wait for 100 ns;

ai <= '1'; bi <= '0';

wait for 100 ns;

ai <= '0'; bi <= '1';

wait for 100 ns;

ai <= '1'; bi <= '1';

wait;

```

```

end process;

```

#### Outline

- Basic Structure of a VHDL Module

- 1) Library Declaration

- 2) Entity Declaration

- External Signal (I/O Pins)

- 3) Architecture Body

- Internal Signal

- Architectural Design Methods

- ① Data Flow Design (concurrent statements)

- ② Structural Design ("port map")

- ③ Behavioral Design (sequential statements)

- Concurrent vs. Sequential Statements

- Design Constructions

# Concurrent vs. Sequential Statements

#### Concurrent Statement

- 1) Statements inside the architecture body can be executed concurrently, except statements enclosed by a process.

- 2) Every statement will be <u>executed once</u> whenever <u>any</u> <u>signal in the right-hand-side of statement changes</u>.

#### Sequential Statement

- 1) Statements within a **process** are executed sequentially, and the result is obtained when the process is complete.

- 2) process (sensitivity list): Whenever any signals in the sensitivity list changes its state, the process executes once.

- 3) A process can be treated as one concurrent statement in the architecture body.

# **Concurrent with Sequential**

- 1 library IEEE; --vivado14.4 ok

- 2 use IEEE.STD\_LOGIC\_1164.ALL;

- 3 entity conc\_ex is

- 4 port (in1,in2,in3: in std\_logic;

- 5 out1,out2 : inout std\_logic);

- 6 end conc\_ex;

- 7 architecture for ex\_arch of conc\_ex is

- 8 begin

- 9 process (in1, in2)

- 10 begin

- 11 out1 <= in1 and in2;</pre>

- 12 end process;

The process (9-12) and line 13 are concurrent and can be interchanged!

- 13 out2 <= out1 and in3; -- concurrent statement

- 14 end for\_ex\_arch;

#### **Class Exercise 1.6**

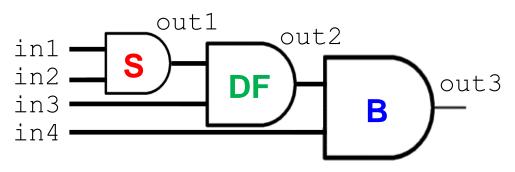

Use structural, data flow, and behavioral designs to implement the following circuit in VHDL:

#### Outline

- Basic Structure of a VHDL Module

- 1) Library Declaration

- 2) Entity Declaration

- External Signal (I/O Pins)

- 3) Architecture Body

- Internal Signal

- Architectural Design Methods

- ① Data Flow Design (concurrent statements)

- ② Structural Design ("port map")

- ③ Behavioral Design (sequential statements)

- Concurrent vs. Sequential Statements

#### Design Constructions

# **Design Constructions**

- Concurrent: Statements that can be stand-alone

- 1) when-else

- Concurrent: **OUTSIDE** process

- 2) with-select-when

- Sequential: Statements inside the process

- 1) if-then-else

- 2) case-when

- 3) for-in-to-loop

Sequential – **INSIDE** process

#### Concurrent 1) when-else

1 library IEEE; 2 use IEEE.STD LOGIC 1164.ALL; 3 entity when ex is 4 port (in1, in2 : in std logic; 5 out1 : out std logic); 6 end when ex; 7 architecture when ex arch of when ex is Condition based 8 begin out1 <= '1' when in1 = '1' and in2 = '1' else '0'; 9 10 end when ex arch; when **condition** is true then out1 <= '1' otherwise then out1 <= '0'

### **Concurrent 2)** with-select-when

- 1 library IEEE;

- 2 use IEEE.STD LOGIC 1164.ALL;

- 3 entity when\_ex is

- 4 port (in1, in2 : in std\_logic;

- 5 out1 : out std\_logic);

- 6 end when ex;

- 7 architecture when ex arch of when ex is

- 8 begin

- 9 with in1 select Signal based

- 10 out1 <= in2 when '1', ← when in1='1' then out1 <= in2

11 '0' when others; when in1 = other cases

12 end when ex arch; then out1 <= '0'</pre>

- Concurrent 1) when-else: Condition based

out1 <= '1' when in1 = '1' and in2 = '1' else '0';</li>

when in1='1' and in2='1' then out1 <= '1', otherwise out <= '0'</li>

- Concurrent 2) with-select-when: Signal based

# **Design Constructions**

- Concurrent: Statements that can be stand-alone

- 1) when-else

- Concurrent: **OUTSIDE** process

- 2) with-select-when

- Sequential: Statements inside the process

- 1) if-then-else

- 2) case-when

- 3) for-in-to-loop

Sequential – **INSIDE** process

#### Sequential 1) if-then-else

in1 out1 in2 entity if ex is port(in1,in2: in std logic; out1: out std logic); end if ex; architecture if ex arch of if ex is begin process (b) begin **if** in1 = '1' and in2 = '1' **then** out1 <= '1'; else out1 <= '0'; end if; end process; end if ex arch;

CENG3430 Lec01: Introduction to VHDL 2022-23 T2

if (cond) then statement; end if; if (cond) then statement1; else statement2; end if; if (cond1) then statement1; elsif (cond2) then statement2; elsif ... else statementn; end if;

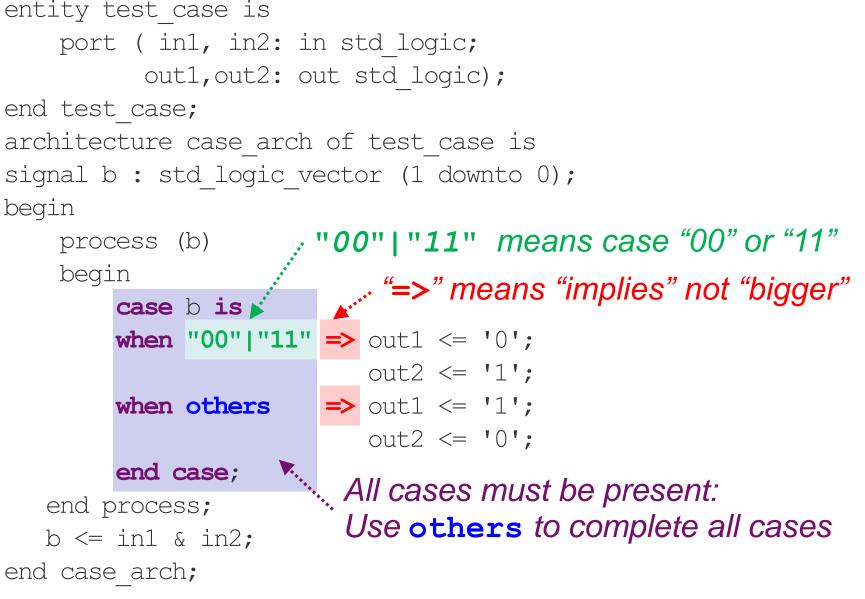

# Sequential 2) case-when

#### Concurrent vs. Sequential Constructions

| 104 | Ex   |

|-----|------|

| 20  | SA - |

|     | 201  |

|     | R HO |

| Concurrent                                  | Sequential                                                                 |

|---------------------------------------------|----------------------------------------------------------------------------|

| when-else                                   | if-then-else                                                               |

| b <= "1000" when a = "00" else              | if a = "00" then b <= "1000"                                               |

| "0100" when <b>a = "01</b> " else           | elsif <b>a = "01</b> " then <b>b &lt;= "1000"</b>                          |

| "0010" when <b>a = "10</b> " else           | elsif <b>a = "10"</b> then <b>b &lt;= "1000"</b>                           |

| "0001" when <b>a = "11";</b>                | else b <= "1000"                                                           |

|                                             | end if;                                                                    |

| with-select-when                            | case-when                                                                  |

| with a select                               | case a is                                                                  |

|                                             |                                                                            |

| $b \ll "1000"$ when "00",                   | when "00" => b <= "1000";                                                  |

|                                             |                                                                            |

| b <= "1000" when "00",                      | when "00" => b <= "1000";                                                  |

| b <= "1000" when "00",<br>"0100" when "01", | <pre>when "00" =&gt; b &lt;= "1000"; when "01" =&gt; b &lt;= "0100";</pre> |

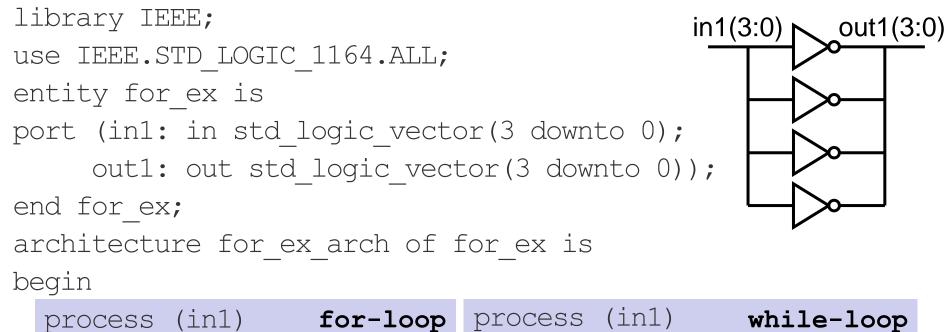

# Sequential 3) 100p (1/2)

```

begin

for i in 0 to 3 loop

out1(i) <= not in1(i);

end loop;

end process;

end for_ex_arch;

CENG3430 Lec01: Introduction to VHDL 2022-23 T2

variable i: integer := 0;

begin

i := 0;

while i < 4 loop

out1(i) <= not in1(i);

i := i + 1;

end loop;

end process;

end process;

```

56

# Sequential 3) 100p (2/2)

• for-loop

for i in 0 to 3 loop

out1(i) <= not in1(i);

end loop;</pre>

- No need to declare the loop index (e.g., i).

- It is implicitly declared within the loop.

- It may not be modified within the loop (e.g., i := i-1;).

- for-loop is generally

supported for synthesis.

CENG3430 Lec01: Introduction to VHDL 2022-23 T2

while-loop

variable i: integer:=0;

...

while i < 4 loop

out1(i) <= not in1(i);

...

end loop;</pre>

- The while loop repeats if the <u>condition</u> tested is true.

- The condition is tested before each iteration.

- while-loop is supported

by some logic synthesis

tools with restrictions.

https://www.ics.uci.edu/~jmoorkan/vhdlref/for\_loop.html https://www.ics.uci.edu/~jmoorkan/vhdlref/while.html

# Variable Object

#### variable VAR\_NAME: <type> [:= <value>];

Note: Variables can be declared without initialized values.

- Examples:

- variable VAR\_NAME: STD\_LOGIC;

- Declared without initialized value

- variable VAR\_NAME : STD\_LOGIC := '1';

- Variables can only be declared/used in the process.

- Variables are used only by programmers for internal representation (less direct relationship to hardware).

# Signal vs. Variable Assignment

- Both signals and variables can be declared without initialized values.

- signal SIG\_NAME: <type> [:= <value>];

- variable VAR\_NAME: <type> [:= <value>];

- Their values can be assigned after declaration.

– Syntax of signal assignment:

SIG\_NAME <= <expression>;

– Syntax of variable assignment:

VAR NAME := <expression>;

# Summary

- Basic Structure of a VHDL Module

- 1) Library Declaration

- 2) Entity Declaration

- External Signal (I/O Pins)

- 3) Architecture Body

- Internal Signal

- Architectural Design Methods

- ① Data Flow Design (concurrent statements)

- ② Structural Design ("port map")

- ③ Behavioral Design (sequential statements)

- Concurrent vs. Sequential Statements

- Design Constructions